fft processor chip

Because each 9124 IC can process the 4096-point FFT in 312 ms says Fleming a three-chip system based around such an architecture will take approximately 104 ms--a speedup of three times Board-level support. This paper describes in detail the design of a CMOS custom fast Fourier transform FFT processor for computing a 256-point complex FFT.

Pdf Fast Performance Pipeline Re Configurable Fft Processor Based On Radix 22 For Variable Length N Semantic Scholar

The FFT butterfly processor reported here consists of one parallel-parallel multiplier and two adders.

. The resulting programmable solution is scalable for the order of the. Calculates 2 to 256 point DFTs on up to 24-bit input data in each I and Q with 24-bit complex outputs. And the final design of a 64-point FFTIFFT processor for the above-mentioned standard is suggested.

Specifications of the FFT co-processor chip. DFT is a method to analyze and process signals and systems. The BU of this architecture is 1889 smaller and 513 faster as compared with smallest and fastest BU reported previously.

Im looking for a processor that can perform a 1024-point FFT on a 50ms time window in real-time. 𝐴𝑇 2 𝑛𝑜𝑟𝑚 Dp mm2 ns2 mW of proposed processor is 137. PMOS thresholds are 930 mV and NMOS thresholds are 680 mV.

The chip which has been successfully fabricated and tested performs a forward and inverse 64-point FFT on a complex twos complement data set in 23 clock cycles making it suitable for high-speed data communication systems like IEEE 80211a. This article discusses techniques to optimize the Fast Fourier Transform FFT for Intel Processor Graphics without using Shared Local Memory SLM or vendor extensions. Salsano Send me a link you know of.

It is characterized with real-time non-stopping processing as the data sequence passing the processor. It realizes the analysis of signals and systems from the frequency domain which analyzes complex signals and systems more conveniently and intuitively. 44 rows Austek A41102 single chip 256-point complex FFT processor.

It is an AT2 non-optimal approach with AT2. I need guidance on how to go about selecting a processor that will do this. The hardware chip performance analysis of the variable length FFT processor architectures on Field Programmable Gate Array FPGA platform using VHDL programming in which FFT length varies from 8 point to 65536 point is focused on.

Contents hide 1 Typical characteristics 2 Architectural features 21 Program flow. Choose the best algorithm for a. The FFT is a class of efficient DFT implementations that produce results identical to the DFT in far fewer cycles.

The full-custom design contains 460000 transistors and was fabricated in a standard single-poly triple-metal CMOS process using 07 m design rules with m. In extended microcon-troller mode the PIC17C42 has 2K x 16 0000h07FFh on-chip program memory space and is capable of. The research article focuses on the hardware chip performance analysis of the variable length FFT processor architectures on Field Programmable Gate Array FPGA platform using VHDL programming in.

ABSTRACT The Fast Fourier Transform FFT is one of the most important algorithm used in digital signal processing DSP. A 1024-point single-chip FFT processor namedSpiffee was designed and fabricated. The Fast Fourier Transform FFT processor is a FFT engine developed for the AT40K family of Field Programmable Gate Arrays FPGAs.

The processor completes one parallel-to-parallel ie when all input data are available in parallel and all output data to-architecture mapping quality exploration is necessary to are generated in parallel 64-point FFT computation in 23 cycles. Performance depends on a deep understanding of how the OpenCL API maps to the. The FFT was used for measuring the bandwidth between processors on a network.

To compute higher point FFTs the data can be stored in the program memory space of the PIC17C42. The Cooley -Tukey algorithm is a widely used FFT algorithm that exploits a divide- and-conquer approach to recursively decompose the DFT computation into smaller and smaller DFT computations until the simplest computation remains. Built as a common parallel bus system with three processors this device can implement a 4096-point FFT as three stages of radix-16.

16-point 24-bit 06um 60MHz 1688mm2 FFT chip by G. 256-point FFTs calculated in 1024 usec. Source publication 6 A Spaceborne Synthetic Aperture Radar Partial Fixed-Point Imaging System Using a Field- Programmable Gate.

The design is based on a decimation-in-frequency radix-2 algorithm and employs in-place computation to opti-mize memory usage. The FFT is well-suited for real-time spectrum analysis in instrumentation and measurement applications. The processor occupies 5985.

The FFT capability of a particular DSP chip or a line of DSP chips - for instance a 6412 running at 300 MHz or at 700 MHz. This FFT processor is synthesized placed and routed for 45 nm technology of nangate open cell library. Pipeline FFT processor is a specified class of proces- sors for DFT computation utilizing fast algorithms.

The Fast Fourier Transform FFT is a fast algorithm of the Discrete Fourier Transform DFT. FFT PROCESSOR Digital signal processor From Wikipedia the free encyclopedia Jump to. FFT is also a good example of a communication-intensive parallel application with complex communication patterns and allows the demonstration of a number of useful parallel coding techniques in particular how to write a distributed array program that succinctly and efficiently implements.

The hardware cost metric ie. At 33 V it operates at 173 MHz---which is a clock rate 26 times greater than the previously fastest rate. Navigation search A digital signal processor DSP is a specialized microprocessor designed specifically for digital signal processing generally in real-time computing.

This paper presents a high performance FFT ASIP that adopts a vectorial ultra-long instruction word ULIW approach and is scalable for the order of the FFT and capable of satisfying performance requirements of various OFDM wireless standards. The implementation leverages a runtime code generator to support a wide variety of FFT dimensions. In order to operate the processor data must first be loaded into the internal RAM.

At a supply voltage of 11 V it calculates a 1024-point complex FFT in 330 s while consuming 95 mW resulting in an adjusted energy efficiency more than 16 times greater than the previously most efficient known FFT processor. The PIC17C42 has instructions TABLRD TABLWT to transfer data between program memory space and on-chip file registers. This paper presents a high performance FFT ASIP.

Dft With Fft Algorithm Using Tms320c67xx Dsp Processor Youtube

A Prototype Analog Mixed Signal Fast Fourier Transform Processor Ic For Ofdm Receivers Semantic Scholar

Design Of Radix 2 64 Point Fft Processor Using Cordic Algorithm Semantic Scholar

Architecture Of Fft Processor Download Scientific Diagram

Block Diagram Of The Proposed Fft Processor Download Scientific Diagram

Pdf Vlsi Design Of Low Cost And High Precision Fixed Point Reconfigurable Fft Processors Semantic Scholar

Pdf Area Efficient 128 Point Fft Processor Using Mixed Radix 4 2 For Ofdm Applications Semantic Scholar

1 Tabular Comparison Of Fft Processor Performance Download Table

Chip Microphotograph Of The Proposed Fft Processor Download Scientific Diagram

Architecture Of Fft Processor Download Scientific Diagram

Fft Processor With Radix Ii Burst I O Architecture 13 Download Scientific Diagram

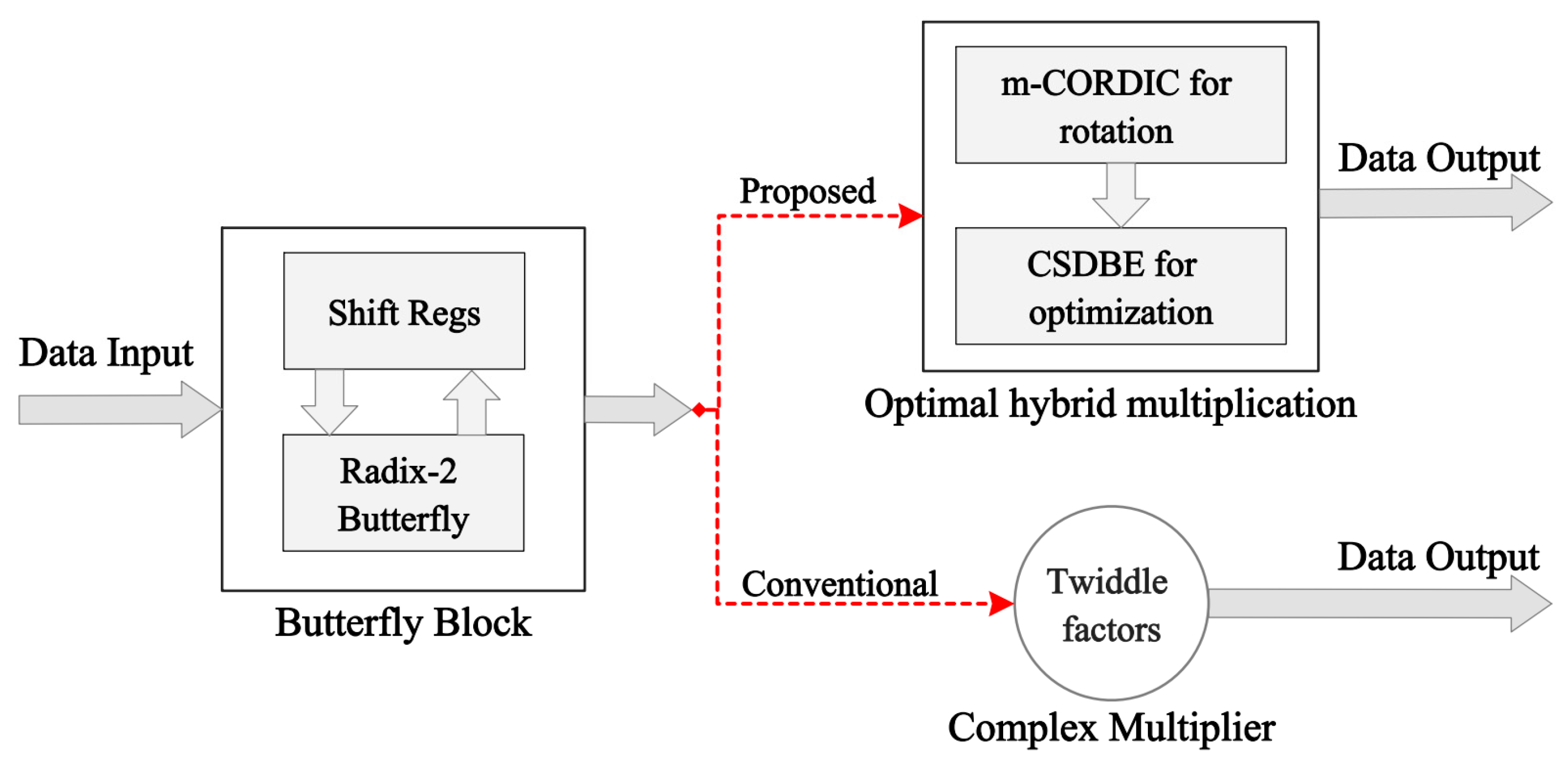

Electronics Free Full Text A Pipelined Fft Processor Using An Optimal Hybrid Rotation Scheme For Complex Multiplication Design Fpga Implementation And Analysis Html

Pdf Fast Performance Pipeline Re Configurable Fft Processor Based On Radix 22 For Variable Length N Semantic Scholar

Design And Implementation Of An All Analog Fast Fourier Transform Processor Semantic Scholar

Block Diagram Of The Proposed 64 Point Fft Ifft Processor Download Scientific Diagram

Figure 5 From Design Of 16 Point Radix 4 Fast Fourier Transform In 0 18aµm Cmos Technology Semantic Scholar

Timing Diagram Of The Proposed Sdf Fft Processor For Double Frequency Download Scientific Diagram

A Prototype Analog Mixed Signal Fast Fourier Transform Processor Ic For Ofdm Receivers Semantic Scholar

Comments

Post a Comment